Simple 8-bit CPU composed of 74LS series and PLD devices, Harvard architecture, 64K ROM + 64K RAM, external bus with standard 8080 timing

Designed by Denjhang's Retro Hardware in Malaysia

Buy with confidence.

Our Tindie Guarantee protects your purchase from fraud. Learn More

What is it? This project is a DIY simple 8-bit CPU project. Basic CPU performance: Speed: 1Hz-2.048MHz, 3T-5T single cycle, most instructions are 5T, a few are 3T (equivalent to 400,000 additions per…

Read More…This project is a DIY simple 8-bit CPU project.

Basic CPU performance:

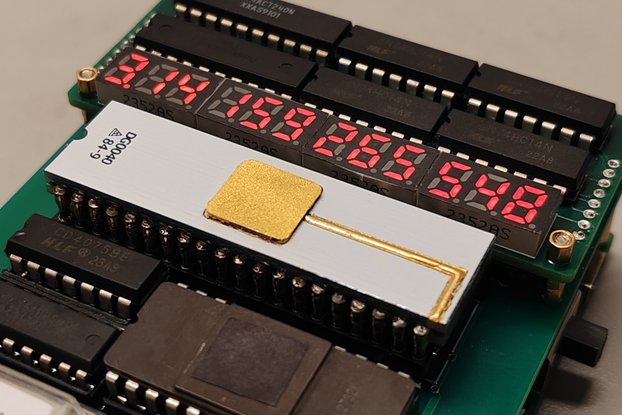

Speed: 1Hz-2.048MHz, 3T-5T single cycle, most instructions are 5T, a few are 3T (equivalent to 400,000 additions per second)

ROM: 64KB (or 32KB)

RAM: 64KB

Bus and ALU bit width: 8

Instruction length (with immediate value): 16

Pointer stack: 4-level 16bit

Hardware interrupt: single-level, 255 vector half interrupt (Note: some instructions are not supported in the interrupt function)

Graphics card: None

Keyboard: None

External bus: 8080 timing, 64KB

The block diagram is as follows:

The architecture refers to the 8008 CPU released by Intel in 1972, using a single internal bus, the instruction set is basically based on 8008, the operation and logic instructions are similar, and there are 4 flag registers.

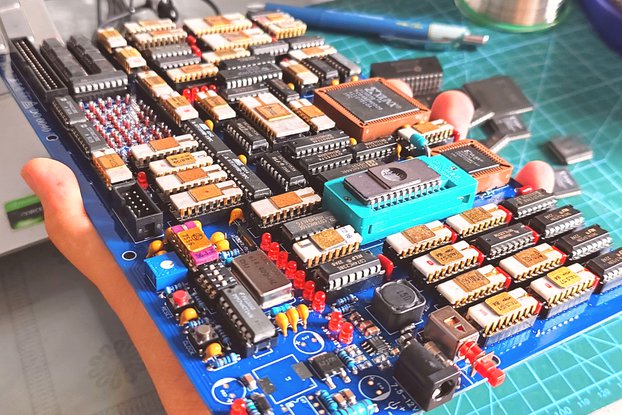

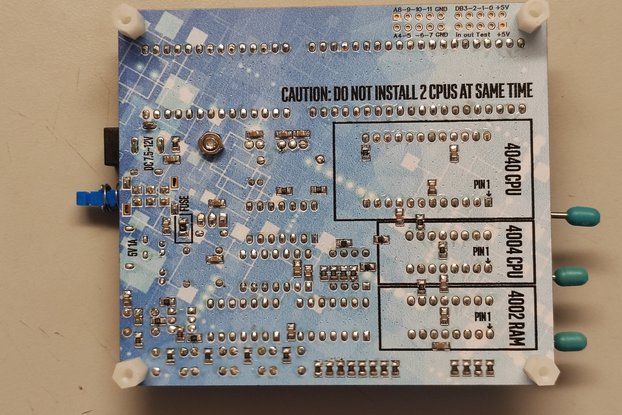

Since the original 8008 uses the CDIP-18 package and has tricky timing, this design first separates the address and data lines of the external bus, and then expands the 16KB addressing range to a 64KB+64KB Harvard structure, but does not support jumping to RAM for execution during program execution. The design mainly consists of the following parts:

The clock source part uses four sources, namely: 1Hz low frequency generated by 7556, 25Hz low frequency, manual button signal, 8224 generates 2.048MHz high frequency clock source, and can be switched arbitrarily in the hardware circuit. The reset circuit has a power-on reset function. Since there is HLT (stop) in the instruction, there is a READY button on the board for easy debugging.

The ALU uses the N8260 operation unit of Signetics, which has three operation functions: full addition, AND gate, and XOR. With the assistance of the additional 74LS86 XOR gate and 74LS153 MUX, it has subtraction, XOR, logical shift, comparison and other functions. ALU sets up a separate AB register, which has no connection with the AB register on the main register stack. There are four FLAGs, namely: CF SF ZF PF. When there is a carry in addition or a borrow in subtraction, CF<=1; when the output number is 0x00/00000000, ZF<=1; when the highest bit/sign bit of the output is 1, SF<=1; when there are an even number of 1s in the output 8 bytes, PF<= 1.

ABCDEFXY 8 general registers without special functions, P register (internal RAM pointer), internal RAM mapping, DPTRH, DPTRL, INDEX three registers, pointing to external RAM unit, pointer calculation formula: 256*DPTRH + DPTRL + INDEX, external RAM mapping (read and write operations are the same as internal registers), PC register (two registers but one mapping, two 8-bit write 16-bit operations are realized through blocking series connection), input port mapping only, AF register bidirectional IO port mapping (similar to the IO port address mapping of 51 single-chip microcomputer)

0000-FFFF addressing operation can be realized, and PC+1 is obtained for each 8-bit program instruction. When the JMP instruction is executed, the high and low 8 bits of the PC register are pushed into the PC, and the original 16-bit process is discarded. In CAL, the high and low 8 bits of the PC are pushed into the PC, and the 16-bit process in the original PC is pushed into the pointer stack. In the RET instruction, the top 16-bit data of the pointer stack is pushed into the PC, and the original process in the PC is discarded.

A very imperfect interrupt mechanism, which can only do some simple operations, no register status recovery, no PSW save and restore, and is not recommended for use

The controller consists of 4 GAL16V8/ATF16V8 chips, with a simple structure, details omitted

Instruction set:

NOP idle run

HLT shutdown

HLTDMA (DMA controllable shutdown)

ADD/ADC/ADDI/ADCI (addition/full addition with/without immediate data)

SUB/SBC/SUBI/SBCI (subtraction with/without immediate data/subtraction with borrow)

NXR/NXRI exclusive or

XOR exclusive or

AND/ANDI bitwise and

CMP/CMPI comparison

RR/RL right shift/left shift with 0 complement

RRC/RLC right shift/left shift with carry complement

JMP/JMC/JNC/JMZ.... (jump/jump when CF=1/jump when CF=0.... other flags are similar)

CAL/CLC/CNC/CLZ.... (sub-function call/call when CF=1/call when CF=0.... other flags are similar)

RET/RTC/RNC/RTZ.... (sub-function return/return when CF=1/return when CF=0.... other flags are similar)

There is no assembler at present. The machine code structure is shown in PDF and the figure above. This instruction set is very friendly to handwritten assembly.

No country selected, please select your country to see shipping options.

No rates are available for shipping to .

Enter your email address if you'd like to be notified when DJS-08 8-bit CISC TTL Computer can be shipped to you:

Thanks! We'll let you know when the seller adds shipping rates for your country.

| Shipping Rate | Tracked | Ships From | First Item | Additional Items |

|---|---|---|---|---|

|

:

|

encourage buyers to pay for insured rates

Buy with confidence.

Our Tindie Guarantee protects your purchase from fraud. Learn More

Kuala Lumpur, Federal Territory of Kuala Lumpur, Malaysia

42 Reviews | 307 Orders

$798.00

Free Shipping!

$599.00

Free Shipping!

$399.00

Free Shipping!

$999.00

Free Shipping!

$225.00

Free Shipping!

$237.00

Free Shipping!

$99.00

Free Shipping!

$399.00

Free Shipping!

By clicking Register, you confirm that you accept our Terms & Conditions

We recognize our top users by making them a Tindarian. Tindarians have access to secret & unreleased features.

We look for the most active & best members of the Tindie community, and invite them to join. There isn't a selection process or form to fill out. The only way to become a Tindarian is by being a nice & active member of the Tindie community!